# Freescale Semiconductor

Advance Information

# **Ultra-Mobile Platform PMIC**

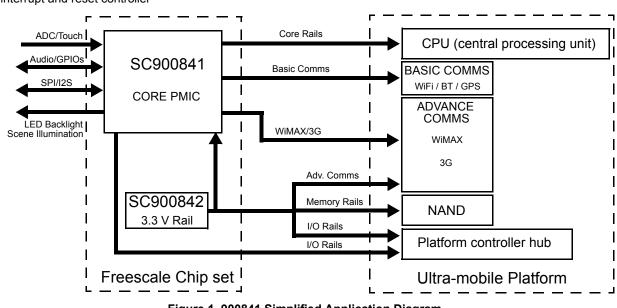

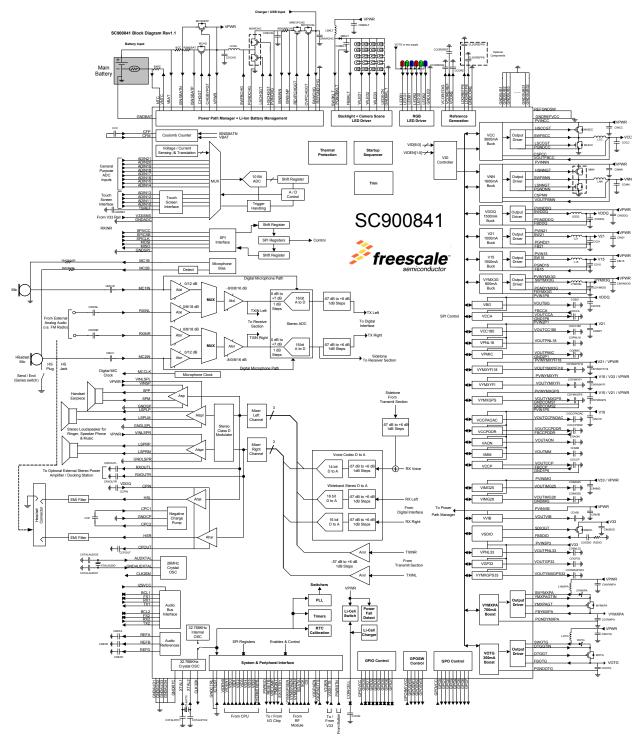

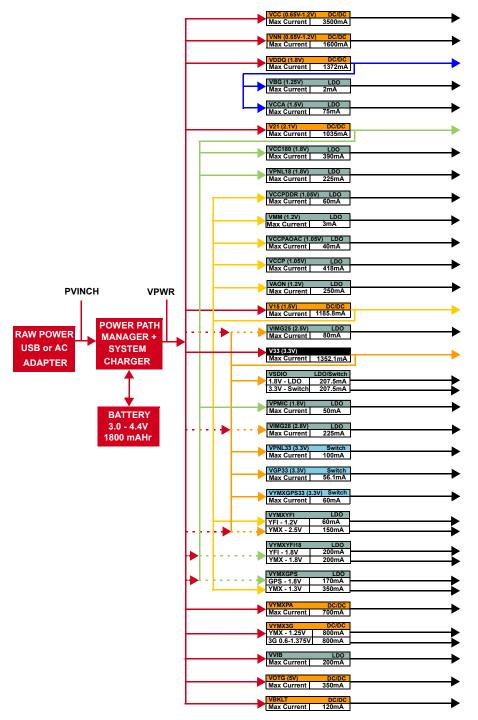

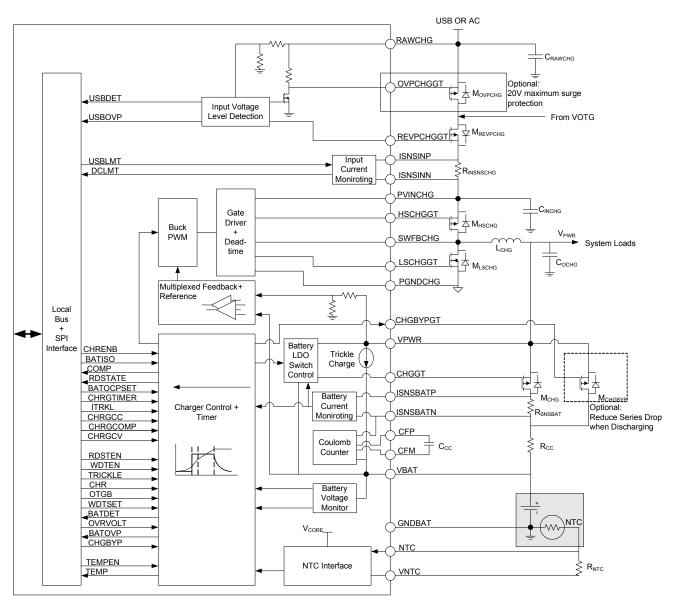

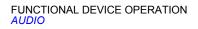

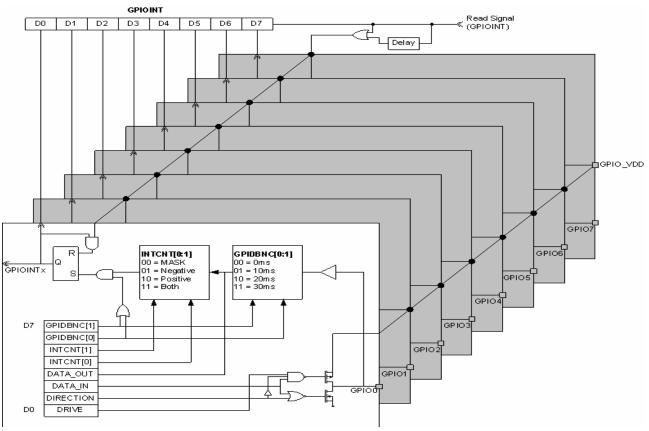

The 900841 is a high-efficiency, Power Management Integrated Circuit (PMIC), capable of providing all operating voltages for ultramobile platforms through its 29 voltage rails. It has nine switching power supplies running at frequencies from 1.0 to 4.0 MHz,17 highly-efficient LDOs and three, 3.3 V power switches. It incorporates a switching mode Li-lon battery charger, advanced audio path, signaling and backlight LED drivers, 22-channel ADC, real time clock, 8 GPIO, 8 GPO, and 4 GPOSW for specific platform switches control.

The SC900841 is fully configurable and controllable through its SPI and Mini SPI interfaces. Along with companion chip SC900842, it provides an optimized power management solution for ultra-mobile platforms used on Mobile Internet Devices (MID), netbooks, tablets, slates, smart phones and other high-tech portable devices.

Optimum partitioning, high feature integration, and state-of-the-art technology allow Freescale to effectively serve this growing market segment.

#### Features

- Complete system power management, battery charging and audio support integrated in a single chip

- Advanced audio path

- Fully programmable DC/DC switching, low drop-out regulators, and load switches

- Power path management & switching mode Li-Ion/Li-Polymer battery charger

- · LCD backlight and system lighting support

- SPI interface (up to 25 MHz operation)

- 22-channel (32 capable) 10-bit ADC for internal and external sensing with touch screen interface

- Real time clock (RTC)

- 8 Interrupt capable GPIOs and 8 GPOs

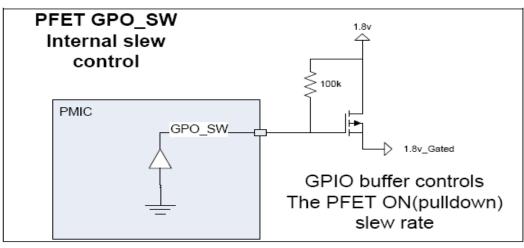

- 4 GPOs for controlling platform switches

- I/O interrupt and reset controller

# 900841

## POWER MANAGEMENT

#### ORDERING INFORMATION

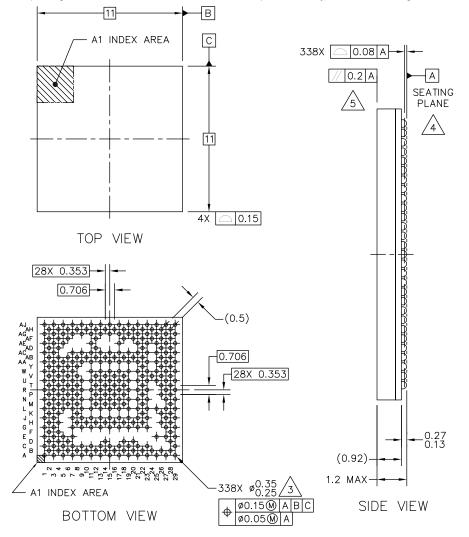

| Device         | Temperature<br>Range (T <sub>A</sub> ) | Package    |  |  |

|----------------|----------------------------------------|------------|--|--|

| SC900841JVK/R2 | -40°C to 85°C                          | 338-MAPBGA |  |  |

#### Applications

- Mobile Internet Devices (MID)

- Tablet PC

- Netbooks

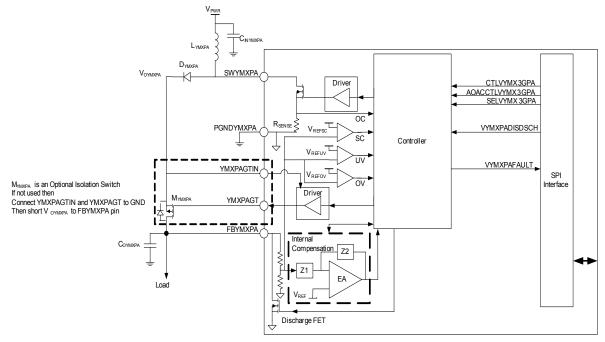

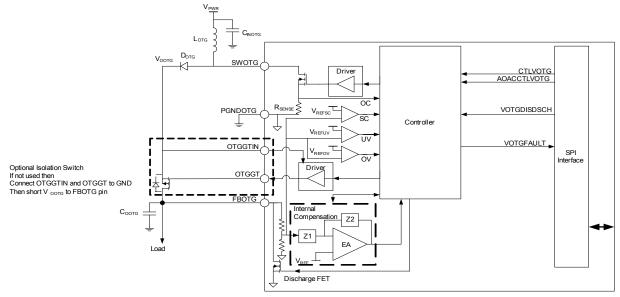

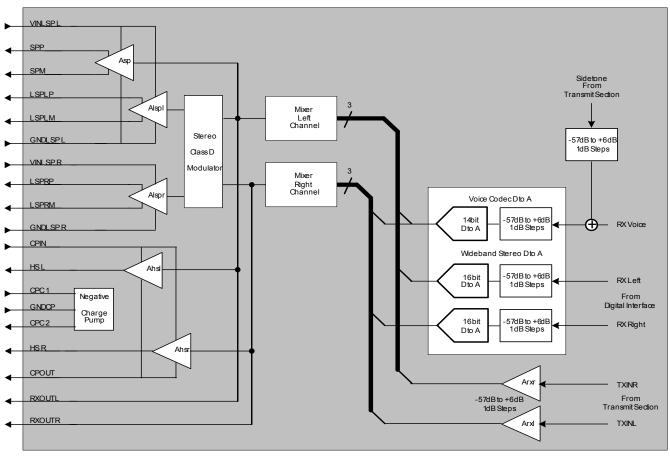

Figure 1. 900841 Simplified Application Diagram

\* This document contains certain information on a new product. Specifications and information herein are subject to change without notice. © Freescale Semiconductor, Inc., 2011. All rights reserved.

Document Number: SC900841 Rev. 2.0, 2/2011

**VRoHS**

# ELECTRICAL CHARACTERISTICS

## **MAXIMUM RATINGS**

#### Table 1. Maximum Ratings

All voltages are with respect to ground, unless otherwise noted. Exceeding these ratings may cause malfunction or permanent damage to the device. The detailed maximum voltage rating per pin can be found in the pin list section.

| Ratings                                                             | Symbol              | Value        | Unit |

|---------------------------------------------------------------------|---------------------|--------------|------|

| ELECTRICAL RATINGS                                                  |                     |              | •    |

| Charger Input Voltage                                               | -                   | -0.3 to +20  | V    |

| LCD Backlight Circuitry Voltage                                     | -                   | -0.3 to +28  | V    |

| Battery Voltage                                                     | -                   | -0.3 to +4.4 | V    |

| Coin Cell Voltage                                                   | -                   | -0.3 to +3.6 | V    |

| ESD Rating, All Pins, Human Body Model (HBM) <sup>(3)</sup>         | V <sub>ESDHBM</sub> | ±2000        | V    |

| ESD Rating, All Pins, Charge Device Model (CDM) <sup>(3), (4)</sup> | V <sub>ESDCDM</sub> | ±450         | V    |

#### THERMAL RATINGS

| Ambient Operating Temperature Range                 | T <sub>A</sub>    | -40 to +85  | °C |

|-----------------------------------------------------|-------------------|-------------|----|

| Operating Junction Temperature Range                | TJ                | -30 to +125 | °C |

| Storage Temperature Range                           | T <sub>ST</sub>   | -65 to +150 | °C |

| Peak Package Reflow Temperature <sup>(1), (2)</sup> | T <sub>PPRT</sub> | 260         | °C |

Notes

1. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause a malfunction or permanent damage to the device.

- 2. Freescale's Package Reflow capability meets the Pb-free requirements for JEDEC standard J-STD-020C, for Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL)

- 3. ESD testing is performed in accordance with the Human Body Model (HBM) (CZAP = 100 pF, RZAP = 1500 Ω), and the Charge Device Model (CDM), Robotic (CZAP = 4.0 pF).

- 4. All pins meet 500 V CDM except VCOREREF.

## **POWER DISSIPATION**

During operation, the temperature of the die must not exceed the maximum junction temperature. Depending on the operating ambient temperature and the total internal dissipation this limit can be exceeded.

To optimize the thermal management scheme and avoid overheating, the 900841 provides a thermal management system that protects against overheating. This protection should be considered as a fail-safe mechanism, and the application design should initiate thermal shutdown under normal conditions. Reference Thermal Management for more details.

## POWER CONSUMPTION

<u>Table 2</u> defines the maximum power consumption specifications in the various system and device states. For each entry in the table, the component is assumed to be configured for driving purely capacitive loads, and the voltages listed in each entry are nominal output voltages.

Note that the "Soft Mechanical Off" state is a transitional state. The device will spend less than 150  $\mu$ s in this state before V15 starts to turn on, upon detection of a valid USB device or valid battery.

## Table 2. Power Rating

| Condition           | Description                                                                                                                                                       | Logic                    | Maximum Power<br>Consumption |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------|

| Hard Mechanical Off | There is no Valid USB device or valid battery connected to SC900841                                                                                               | USBDET = 0<br>BATDET = 0 | 0 mW                         |

| Soft Mechanical Off | SC900841 has input power from either a USB device or a battery. All VRs are programmed "OFF"                                                                      | USBDET = 1<br>BATDET = 0 | 50 mW                        |

|                     |                                                                                                                                                                   | USBDET = 0<br>BATDET = 1 | 5 mW                         |

| Power On            | SC900841 has input power from either a USB device or a battery. The cold-boot rails are "ON".                                                                     | USBDET = 0<br>BATDET = 1 | 100 mW                       |

|                     | V21 = 2.1 V<br>V15 = 1.5 V<br>VAON = 1.2 V<br>VCCPAOAC = 1.05 V<br>VPMIC = 1.8 V<br>All VR outputs are set in PFM or APS mode driving purely capacitive<br>loads. | USBDET = 1<br>BATDET = 0 | 10 mW                        |

## STATIC ELECTRICAL CHARACTERISTICS

## **Table 3. Static Electrical Characteristics**

| Characteristic                                                                                                           | Symbol              | Min                                                                    | Тур         | Мах                                                           | Unit |

|--------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------|-------------|---------------------------------------------------------------|------|

| SYSTEM CONTROL INTERFACE                                                                                                 |                     |                                                                        |             |                                                               |      |

| Input Low Voltage<br>VYMXGPSEN, VYMXPAEN, VYMX3GEN, SDATA, SCK, CS                                                       | V <sub>IL</sub>     | 0                                                                      | _           | 0.3*V <sub>PMIC</sub>                                         | V    |

| EXITSTBY, VID[6:0]<br>THRMTRIPB, VIDEN[1:0]                                                                              |                     | 0<br>0                                                                 | -           | 0.3*V <sub>CCP</sub><br>0.3*V <sub>CCPA</sub>                 |      |

| V33STTS, V3GPASTTS                                                                                                       |                     | 0                                                                      | -           | OAC<br>0.3*V <sub>PMIC</sub>                                  |      |

| Input High Voltage<br>VYMXGPSEN, VYMXPAEN, VYMX3GEN, SDATA, SCK, CS<br>EXITSTBY, VID[6:0]<br>THRMTRIPB, VIDEN[1:0]       | V <sub>IH</sub>     | 0.7*V <sub>PMIC</sub><br>0.7*V <sub>CCP</sub><br>0.7*V <sub>CCPA</sub> | -<br>-<br>- | V <sub>PMIC</sub><br>V <sub>CCP</sub><br>V <sub>CCPAOAC</sub> | V    |

| V33STTS, V3GPASTTS                                                                                                       |                     | oac<br>0.7*V <sub>PMIC</sub>                                           | -           | V <sub>PMIC</sub>                                             |      |

| Output Low Voltage<br>PMICINT, VRCOMP, RESETB, PWRGD, V33EN, V3GPAEN                                                     | V <sub>OL</sub>     | 0                                                                      | -           | 0.1                                                           | V    |

| Output High Voltage<br>PMICINT, VRCOMP, RESETB, PWRGD, V33EN, V3GPAEN                                                    | V <sub>OH</sub>     | V <sub>PMIC</sub> - 0.1                                                | -           | V <sub>PMIC</sub>                                             | V    |

| SPI INTERFACE LOGIC IO                                                                                                   |                     |                                                                        |             |                                                               |      |

| Operating Voltage Range (SPIVCC Pin)                                                                                     | V <sub>SPIVCC</sub> | 1.74                                                                   | 1.8         | 3.1                                                           | V    |

| Input High SPICSB, MOSI, SPICLK                                                                                          | -                   | 0.7*<br>V <sub>SPIVCC</sub>                                            | -           | V <sub>SPIVCC</sub><br>+0.3                                   | V    |

| Input Low SPICSB, MOSI, SPICLK                                                                                           | -                   | 0                                                                      | -           | 0.3*<br>V <sub>SPIVCC</sub>                                   | V    |

| Output Low MISO<br>(Output sink 100 μA)                                                                                  | -                   | 0                                                                      | -           | 0.1                                                           | V    |

| Output High MISO<br>(Output source 100 μA)                                                                               | -                   | V <sub>SPIVCC</sub><br>-0.1                                            | -           | V <sub>SPIVCC</sub>                                           | V    |

| OSCILLATOR AND CLOCK OUTPUTS MAIN CHARACTERISTICS                                                                        |                     |                                                                        |             |                                                               |      |

| Operating Voltage                                                                                                        | -                   | 1.2                                                                    | -           | 1.5                                                           | V    |

| RTC OSC Consumption Current (RTC Mode: All blocks disabled, no main battery attached, coin cell is attached to COINCELL) | -                   | -                                                                      | 1.0         | 2.0                                                           | μA   |

| 26 MHz OSC Consumption Current                                                                                           | -                   | -                                                                      | -           | 500                                                           | μA   |

| Output Low CLK32K & CLK26M (Output sink 100 µA)                                                                          | -                   | 0                                                                      | -           | 0.1                                                           | V    |

| Output High CLK32K & CLK26M (Output source 100 µA)                                                                       | -                   | V <sub>SPIVCC</sub> - 0.1                                              | -           | V <sub>SPIVCC</sub>                                           | V    |

| CLK32K & CLK26M Output Duty Cycle                                                                                        | -                   | 40                                                                     | 50          | 60                                                            | %    |

## **Table 3. Static Electrical Characteristics**

$T_A$  = -40 °C to 85 °C,  $V_{PWR}$  = 3.0 to 4.4 V, typical external component values, and full load current range, unless otherwise noted. Typical values are characterized at  $V_{PWR}$  = 3.6 V and 25 °C.

| Characteristic                                                                                                             | Symbol                        | Min  | Тур  | Мах  | Unit         |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------|------|------|------|--------------|

| RTC                                                                                                                        |                               |      |      |      |              |

| Input Voltage Range                                                                                                        | -                             | 1.2  | -    | 1.5  | V            |

| Consumption Current                                                                                                        | -                             | -    | 15   | 25   | μA           |

| Crystal OSC Frequency Tolerance                                                                                            | -                             | -30  | -    | +30  | ppm          |

| Crystal OSC Peak Temperature Frequency (Turn Over Temperature)                                                             | -                             | 20   | 25   | 30   | °C           |

| Crystal OSC Maximum Series Resistance                                                                                      | -                             | -    | 80   | -    | KΩ           |

| Crystal OSC Maximum Drive Level                                                                                            | -                             | -    | 0.5  | -    | μW           |

| Crystal OSC Operating Drive Level                                                                                          | -                             | 0.25 | -    | 0.5  | μW           |

| Crystal OSC Nominal Lead Capacitance                                                                                       | -                             | -    | 9.0  | -    | pF           |

| Crystal OSC Aging                                                                                                          | -                             | -    | -    | 3    | ppm/<br>year |

| COIN CELL CHARGER                                                                                                          |                               |      |      |      |              |

| Coin cell Charge Voltage (Selectable through VCOIN[2:0] bits)                                                              | V <sub>COINCELL</sub>         | 2.5  | -    | 3.3  | V            |

| Coin cell Charge Voltage Accuracy                                                                                          | -                             | -100 | -    | 100  | mV           |

| Coin cell Charge Current                                                                                                   | I <sub>COIN</sub>             | -    | 60   | -    | μA           |

| Coin cell Charge Current Accuracy                                                                                          | -                             | -15  | -    | 15   | %            |

| POWER STATES DETECTION THRESHOLDS                                                                                          |                               |      | •    |      |              |

| Input Voltage Rising Detection Threshold                                                                                   | V <sub>RAWCHGDET</sub>        | -    | -    | 4.50 | V            |

| Input Voltage Rising Detection Threshold Hysteresis                                                                        | V <sub>RAWCHGDETHY</sub><br>S | -    | 100  | -    | mV           |

| Battery Cutoff Threshold (Depending on Battery Model)                                                                      | VBATOFF                       | 2.2  | -    | 2.4  | V            |

| Coin Cell Disconnect Threshold                                                                                             | V <sub>COINOFF</sub>          | 1.8  | -    | 2.0  | V            |

| Low Battery Threshold                                                                                                      | V <sub>LOWBAT</sub>           | 3.2  | -    | -    | V            |

| Valid Battery Threshold                                                                                                    | V <sub>TRKL</sub>             | -    | 3.0  | -    | V            |

| VPWR Rising Under-voltage Threshold                                                                                        | V <sub>PWRUVR</sub>           | -    | 3.1  | -    | V            |

| VPWR Falling Under-voltage Threshold                                                                                       | V <sub>PWRUVF</sub>           | -    | 2.55 | -    | V            |

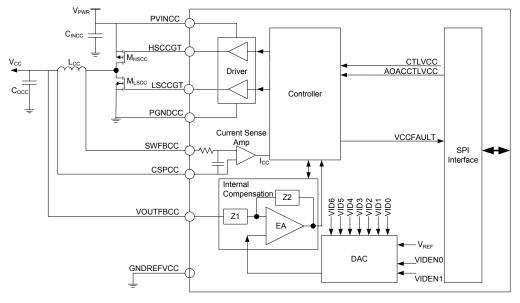

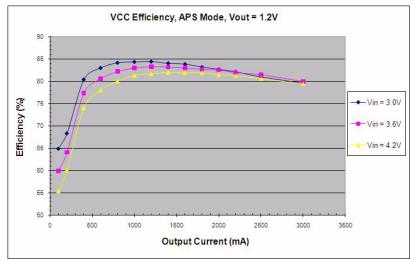

| VCC ELECTRICAL CHARACTERISTICS                                                                                             |                               |      | •    |      |              |

| Input Voltage Range                                                                                                        | V <sub>PWR</sub>              | 3.0  | 3.6  | 4.4  | V            |

| Extended Input Voltage Range                                                                                               | V <sub>PWR</sub>              | 2.8  | 3.6  | 4.7  | V            |

| Output Voltage Programmability Range                                                                                       |                               |      |      |      | V            |

| Low Power Mode                                                                                                             | V <sub>CC</sub>               | 0.3  | -    | 0.7  |              |

| Active Mode                                                                                                                |                               | 0.65 | -    | 1.2  |              |

| Output Voltage Programmability Step Size                                                                                   | -                             | -    | 12.5 | -    | mV           |

| Output Voltage Accuracy                                                                                                    | -                             |      |      |      | %            |

| 0.6 V < V <sub>CC</sub> < 12 V, 1.5 A < I <sub>CC</sub> < 3.5 A                                                            |                               | -5.0 | -    | 5.0  |              |

| $0.6 \text{ V} < \text{V}_{\text{CC}} < 12 \text{ V}, \text{I}_{\text{CC}} < 1.5 \text{ A}$                                |                               | -4.0 | -    | 4.0  |              |

| 0.3 V < V <sub>CC</sub> < 0.6 V                                                                                            |                               | -7.0 | -    | 7.0  |              |

| Output Voltage Overshoot                                                                                                   | V <sub>OS</sub>               |      |      |      | mV           |

| Maximum overshoot voltage above VID setting voltage. Maximum<br>overshoot time is 10-30 s, output voltage = 0.9 V at 50 mA |                               | -    | -    | 50   |              |

900841

### **Table 3. Static Electrical Characteristics**

| Characteristic                                                                                                       | Symbol                  | Min  | Тур      | Max      | Unit |

|----------------------------------------------------------------------------------------------------------------------|-------------------------|------|----------|----------|------|

| Continuous Output Load Current                                                                                       |                         |      |          |          | Α    |

| Low Power mode                                                                                                       | I <sub>CC</sub>         | -    | -        | 0.2      |      |

| Active Mode                                                                                                          |                         | 0.2  | -        | 3.5      |      |

| Peak Current Limit                                                                                                   | ILIMCC                  | -    | 5.0      | -        | А    |

| Output Current Limit Accuracy                                                                                        | -                       |      | ±15      | -        | %    |

| Transient Load Change                                                                                                | Δl <sub>CC</sub>        |      |          |          | Α    |

| Low Power Mode                                                                                                       |                         | -    | -        | 0.2      |      |

| Active Mode                                                                                                          |                         | -    | -        | 1.2      |      |

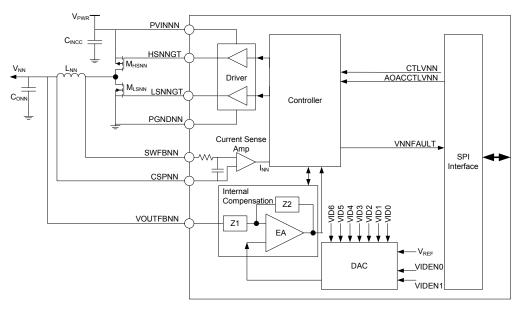

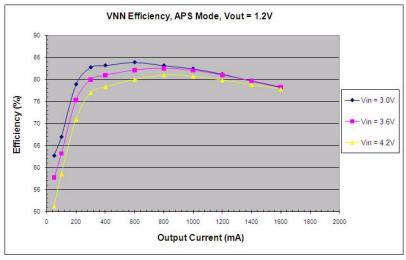

| /NN ELECTRICAL CHARACTERISTICS                                                                                       |                         |      |          |          |      |

| Input Voltage Range                                                                                                  | V <sub>PWR</sub>        | 3.0  | 3.6      | 4.4      | V    |

| Extended Input Voltage Range                                                                                         | V <sub>PWR</sub>        | 2.8  | 3.6      | 4.7      | V    |

| Output Voltage Programmability Range (Set by VID Control Signals)                                                    | V <sub>NN</sub>         | 0.65 | -        | 1.2      | V    |

| Output Voltage Programmability Step Size                                                                             | -                       | -    | 12.5     | -        | mV   |

| Output Voltage Accuracy                                                                                              | -                       | -5.0 | -        | 5.0      | %    |

| Output Voltage Overshoot                                                                                             | V <sub>OS</sub>         | -    | -        | 50       | mV   |

| Maximum overshoot voltage above VID setting voltage. Maximum overshoot time is 10 s, output voltage = 0.9 V at 50 mA |                         |      |          |          |      |

| Continuous Output Load Current                                                                                       | I <sub>NN</sub>         |      |          |          | А    |

| Low Power Mode                                                                                                       |                         | -    | -        | 0.2      |      |

| Active Mode                                                                                                          |                         | 0.2  | -        | 1.6      |      |

| Peak Current Limit                                                                                                   | I <sub>LIMNN</sub>      | -    | 2.5      | -        | А    |

| Output Current Limit Accuracy                                                                                        | -                       | -    | ±20      | -        | %    |

| Transient Load Change                                                                                                | ۵I <sub>NN</sub>        | -    | -        | 0.5      | А    |

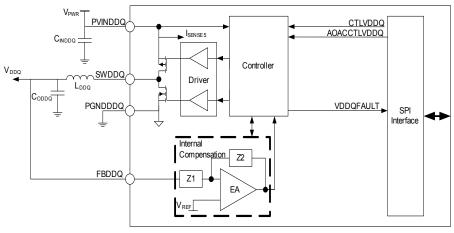

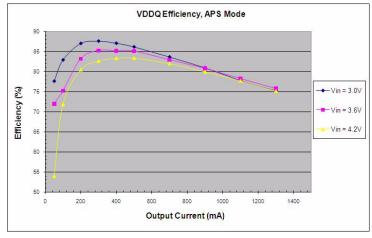

| /DDQ ELECTRICAL CHARACTERISTICS                                                                                      |                         |      |          |          |      |

| Input Voltage Range                                                                                                  | V <sub>PWR</sub>        | 3.0  | 3.6      | 4.4      | V    |

| Extended Input Voltage Range                                                                                         | V <sub>PWR</sub>        | 2.8  | 3.6      | 4.7      | V    |

| Output Voltage Setting                                                                                               | V <sub>DDQ</sub>        | -    | 1.8      | -        | V    |

| Output Voltage Accuracy                                                                                              | -                       | -5.0 | -        | 5.0      | %    |

| Continuous Output Load Current                                                                                       | I <sub>DDQ</sub>        | -    | -        | 1.3      | А    |

| Peak Current Limit                                                                                                   | ILIMDDQ                 | -    | 1.78     | -        | Α    |

| Output Current Limit Accuracy                                                                                        | -                       |      |          |          | %    |

| 0.5 A < I <sub>DDQ</sub> < 1.3 A                                                                                     |                         | -15  | -        | +15      |      |

| $I_{\text{DDQ}} < 0.5 \text{ A}$                                                                                     |                         | -20  | -        | +20      |      |

| Transient Load Change                                                                                                | I <sub>DDQ</sub>        | -    | -        | 0.5      | А    |

| Effective Quiescent Current Consumption (PWM, No Load)                                                               | I <sub>QDDQ</sub>       | -    | 30       | -        | μA   |

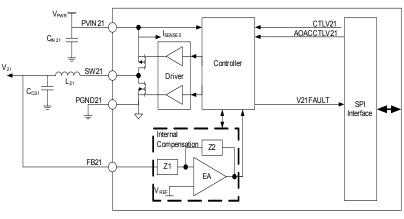

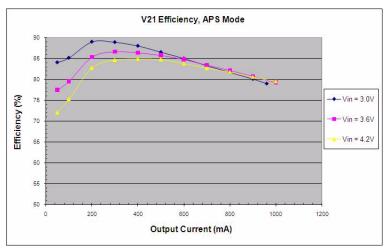

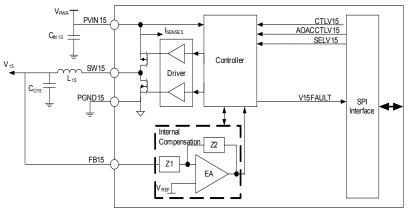

| /21 ELECTRICAL CHARACTERISTICS                                                                                       |                         | 1    | _        | <u> </u> |      |

| Input Voltage Range                                                                                                  | V <sub>PWR</sub>        | 3.0  | 3.6      | 4.4      | V    |

| Extended Input Voltage Range                                                                                         | V <sub>PWR</sub>        | 2.8  | 3.6      | 4.7      | v    |

| Output Voltage Setting                                                                                               | VPWR<br>V <sub>21</sub> | -    | 2.1      | -        | V    |

| Output Voltage Accuracy                                                                                              | ⊻21                     |      | <u> </u> | -        | v    |

## **Table 3. Static Electrical Characteristics**

| Characteristic                                              | Symbol                  | Min    | Тур                        | Max      | Unit |

|-------------------------------------------------------------|-------------------------|--------|----------------------------|----------|------|

| Continuous Output Load Current                              | I <sub>21</sub>         | -      | -                          | 1.0      | А    |

| Peak Current Limit                                          | I <sub>LIM21</sub>      | -      | 1.42                       | -        | Α    |

| Output Current Limit Accuracy                               | -                       | -20    | -                          | +20      | %    |

| Transient Load Change                                       | I <sub>21</sub>         | -      | -                          | 0.5      | А    |

| Effective Quiescent Current Consumption (PWM, No Load)      | I <sub>Q21</sub>        | -      | 30                         | -        | μA   |

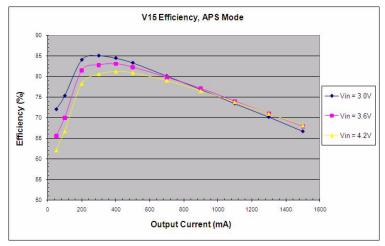

| V15 ELECTRICAL CHARACTERISTICS                              |                         |        |                            |          |      |

| Input Voltage Range                                         | V <sub>PWR</sub>        | 3.0    | 3.6                        | 4.4      | V    |

| Extended Input Voltage Range                                | V <sub>PWR</sub>        | 2.8    | 3.6                        | 4.7      | V    |

| Output Voltage Setting (Also programmable to 1.6 V typical) | V <sub>15</sub>         | -      | 1.5                        | -        | V    |

| Output Voltage Accuracy                                     | -                       | -5.0   | -                          | 5.0      | %    |

| Continuous Output Load Current                              | I <sub>15</sub>         | 0      | 0.75                       | 1.5      | А    |

| Peak Current Limit                                          | I <sub>LIM15</sub>      | -      | 1.6                        | -        | А    |

| Output Current Limit Accuracy                               | -                       | -20    | -                          | +20      | %    |

| Transient Load Change                                       | I <sub>15</sub>         | -      | -                          | 0.5      | А    |

| Effective Quiescent Current Consumption (PWM, No Load)      | I <sub>Q15</sub>        | -      | 30                         | -        | μA   |

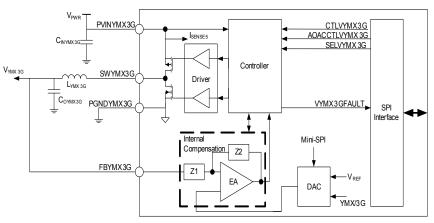

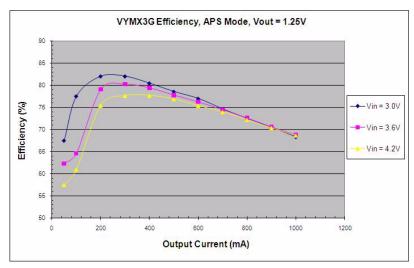

| VYMX3G ELECTRICAL CHARACTERISTICS                           |                         |        | 1                          |          |      |

| Input Voltage Range                                         | V <sub>PWR</sub>        | 3.0    | 3.6                        | 4.4      | V    |

| Extended Input Voltage Range                                | V <sub>PWR</sub>        | 2.8    | 3.6                        | 4.7      | V    |

| Output Voltage Setting                                      | V <sub>YMX3G</sub>      |        |                            |          | V    |

| YMX                                                         |                         | -      | 1.25                       | -        |      |

| 3G (Programmable through Mini-SPI)                          |                         | 0.6    | -                          | 1.375    |      |

| Output Voltage Accuracy                                     | -                       | -5.0   | -                          | 5.0      | %    |

| Output Voltage Ripple (PWM mode)                            | ΔI <sub>YMX3G</sub>     | -10    | -                          | +10      | mV   |

| Continuous Output Load Current                              | I <sub>YMX3G</sub>      | 0      | -                          | 0.8      | А    |

| Peak Current Limit                                          | I <sub>LIMYMX3G</sub>   | -      | 1.46                       | -        | А    |

| Output Current Limit Accuracy                               | -                       | -20    | -                          | +20      | %    |

| Transient Load Change                                       | $\Delta I_{YMX3G}$      | -      | -                          | 0.2      | А    |

| Effective Quiescent Current Consumption (PWM, No Load)      | I <sub>QYMX3G</sub>     | -      | 30                         | -        | μA   |

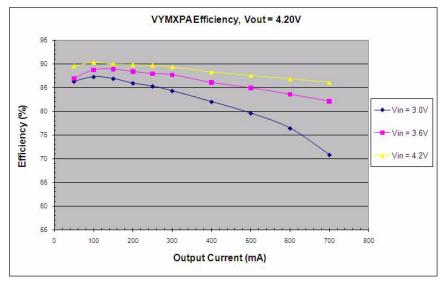

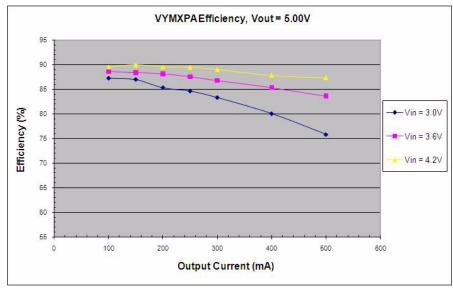

| VYMXPA ELECTRICAL CHARACTERISTICS                           |                         |        |                            |          |      |

| Input Voltage Range                                         | V <sub>PWR</sub>        | 3.0    | 3.6                        | 4.4      | V    |

| Extended Input Voltage Range                                | V <sub>PWR</sub>        | 2.8    | 3.6                        | 4.7      | V    |

| Typical Output Voltage Range                                | V <sub>OYMXPA</sub>     | (Selec | table, see <mark>Ta</mark> | able 37) | V    |

| Output Accuracy                                             | -                       | -5.0   | -                          | +5.0     | %    |

| Output Voltage Ripple                                       | $\Delta V_{YMXPA}$      | -10    | -                          | 10       | mV   |

| Continuous Output Load Current                              | I <sub>OYMXPA</sub>     |        |                            |          | А    |

| V <sub>YMXPA</sub> = 4.2 V                                  |                         | -      | -                          | 0.70     |      |

| V <sub>YMXPA</sub> = 5.0 V                                  |                         | -      | -                          | 0.50     |      |

| Under-voltage Protection Threshold                          | V <sub>UVYMXPA</sub>    | -      | 3.7                        | -        | V    |

| Under-voltage Protection Threshold Hysteresis               | V <sub>UVYMXPAHYS</sub> | -      | 0.2                        | -        | V    |

## **Table 3. Static Electrical Characteristics**

| Characteristic                                                               | Symbol                  | Min  | Тур  | Мах  | Unit |

|------------------------------------------------------------------------------|-------------------------|------|------|------|------|

| Over-voltage Protection Threshold                                            | V <sub>OVYMXPA</sub>    | -    | 5.75 | -    | V    |

| Over-voltage Protection Threshold Hysteresis                                 | V <sub>OVYMXPAHYS</sub> | -    | 0.16 | -    | V    |

| Over-current limit threshold                                                 | I <sub>LIMYMXPA</sub>   | -    | 1.9  | -    | А    |

| Over-current limit threshold Accuracy                                        | -                       | -20  | -    | 20   | %    |

| Short-circuit Protection Threshold (Measured at the output voltage)          | V <sub>SCYMXPA</sub>    | -    | 3.0  | -    | V    |

| Short-circuit Protection Threshold Accuracy (Measured at the output voltage) | -                       | -20  | -    | 20   | %    |

| Transient Load Change (I <sub>OYMXPA</sub> from 1.0 to 201 mA)               | $\Delta I_{YMXPA}$      | -    | -    | 0.2  | А    |

| FBYMXPA Leakage Current                                                      | I <sub>FBYMXPALKG</sub> | -    | 0.1  | -    | μA   |

| YMXPAGTIN Leakage Current                                                    | IYMXPAGTINLKG           | -    | -    | 5.0  | μA   |

| YMXPAGT Leakage Current                                                      | I <sub>YMXPAGTLKG</sub> |      |      |      | μA   |

| V <sub>OL</sub> =100 mV, V <sub>OH</sub> =V <sub>YMXPA</sub> - 100 mV        |                         | -25  | -    | 25   |      |

| Discharge FET Resistance                                                     | R <sub>DSCHYMXPA</sub>  | -    | 45   | -    | Ω    |

| Effective Quiescent Current Consumption (No Load)                            | I <sub>QYMXPA</sub>     | -    | 125  | -    | μA   |

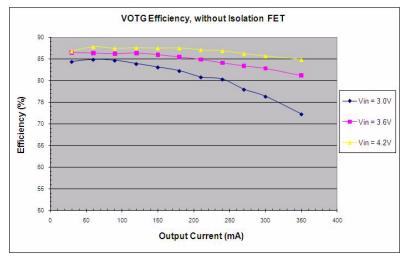

| VOTG ELECTRICAL CHARACTERISTICS                                              |                         |      |      |      |      |

| Input Voltage Range                                                          | V <sub>PWR</sub>        | 3.0  | 3.6  | 4.4  | V    |

| Extended Input Voltage Range                                                 | V <sub>PWR</sub>        | 2.8  | 3.6  | 4.7  | V    |

| Typical Output Voltage Range                                                 | V <sub>OTG</sub>        | -    | 5.0  | -    | V    |

| Output Accuracy                                                              | -                       | -4.0 | -    | +4.0 | %    |

| Continuous Output Load Current                                               | I <sub>OOTG</sub>       | 0    | -    | 0.35 | A    |

| Under-voltage Protection Threshold                                           | V <sub>UVOTG</sub>      | -    | 4.5  | -    | V    |

| Under-voltage Protection Threshold Hysteresis                                | V <sub>UVOTGHYS</sub>   | -    | 0.2  | -    | V    |

| Over-voltage Protection Threshold                                            | V <sub>OVOTG</sub>      | -    | 5.76 | -    | V    |

| Over-voltage Protection Threshold Hysteresis                                 | V <sub>OVOTGHYS</sub>   | -    | 0.16 | -    | V    |

| Over-current limit threshold                                                 | I <sub>LIMOTG</sub>     | -    | 1.5  | -    | A    |

| Over-current limit threshold Accuracy                                        | -                       | -20  | -    | 20   | %    |

| Short-circuit Protection Threshold (Measured at the output voltage)          | V <sub>SCOTG</sub>      | -    | 3.5  | -    | V    |

| Short-circuit Protection Threshold Accuracy (Measured at the output voltage) | -                       | -20  | -    | 20   | %    |

| Transient Load Change (I <sub>OOTG</sub> from 1.0 mA to 201 mA)              | I <sub>OTG</sub>        | -    | -    | 0.2  | A    |

| FBOTG Leakage Current                                                        | I <sub>FBOTGLKG</sub>   | -    | 0.1  | -    | μA   |

| OTGGTIN Leakage Current                                                      | IOTGGTINLKG             | -    | -    | 5.0  | μA   |

| OTGGT Leakage Current                                                        | IOTGGTLKG               | -25  | -    | 25   | μA   |

| Discharge FET Resistance                                                     | R <sub>DSCHOTG</sub>    | -    | 100  | -    | Ω    |

| Effective Quiescent Current Consumption (No Load)                            | I <sub>QOTG</sub>       | -    | 100  | -    | μA   |

## **Table 3. Static Electrical Characteristics**

| Characteristic                                                                            | Symbol                 | Min  | Тур  | Max  | Unit |

|-------------------------------------------------------------------------------------------|------------------------|------|------|------|------|

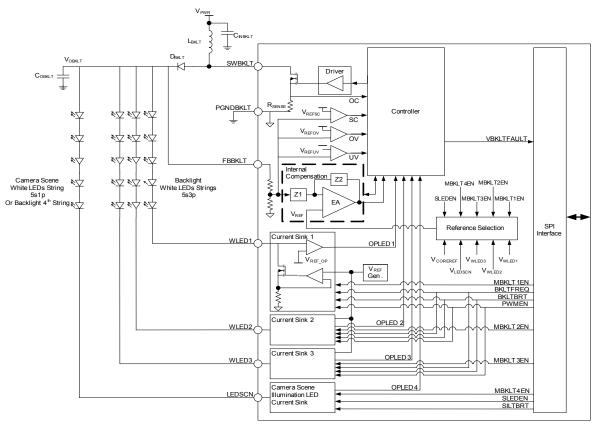

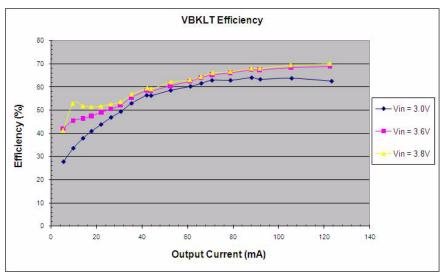

| VBKLT ELECTRICAL CHARACTERISTICS                                                          |                        |      |      | I    |      |

| Input Voltage Range                                                                       | V <sub>PWR</sub>       | 3.0  | 3.6  | 4.4  | V    |

| Extended Input Voltage Range                                                              | V <sub>PWR</sub>       | 2.8  | 3.6  | 4.7  | V    |

| Typical Output Voltage Range                                                              | V <sub>BKLT</sub>      |      |      |      | V    |

| LCD Backlight Active                                                                      |                        | 6.0  | -    | 23   |      |

| Only Camera Scene                                                                         |                        | 21   | 22   | 23   |      |

| Maximum Output Load Current                                                               | I <sub>BKLTMAX</sub>   | -    | -    | 120  | mA   |

| LED Forward Voltage Range                                                                 | V <sub>F</sub>         | -    | -    | 4.0  | V    |

| Under-voltage Detection Threshold                                                         | V <sub>UVBKLT</sub>    | -    | 20   | -    | V    |

| Under-voltage Detection Threshold Hysteresis                                              | V <sub>UVBKLTHYS</sub> | -    | 1.0  | -    | V    |

| Over-voltage Protection Threshold                                                         | V <sub>OVBKLT</sub>    | -    | 24   | -    | V    |

| Over-voltage Protection Threshold Hysteresis                                              | V <sub>OVBKLTHYS</sub> | -    | 1.0  | -    | V    |

| Over-current limit threshold                                                              | I <sub>LIMBKLT</sub>   | -    | 1.9  | -    | А    |

| Over-current limit threshold Accuracy                                                     | -                      | -20  | -    | 20   | %    |

| Short-circuit Protection Threshold (Measured at the output voltage)                       | V <sub>SCBKLT</sub>    | -    | 4.0  | -    | V    |

| Short-circuit Protection Threshold Accuracy (Measured at the output voltage)              | -                      | -20  | -    | 20   | %    |

| LED Current Sink Headroom                                                                 | -                      | 0.4  | 0.5  | 0.6  | mV   |

| FBBKLT Leakage Current                                                                    | I <sub>FBBKLTLKG</sub> | -    | 0.1  | -    | μA   |

| WLEDx and LEDSCN Leakage Current (VBKLT is disabled and current sink is OFF)              | -                      | -    | -    | 1.0  | μA   |

| Effective Quiescent Current Consumption (No Load)                                         | I <sub>QBKLT</sub>     | -    | 500  | -    | μA   |

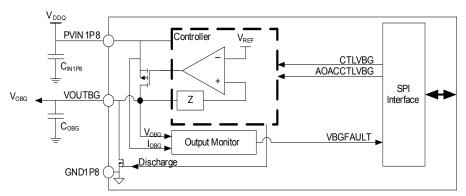

| VBG ELECTRICAL CHARACTERISTICS                                                            |                        |      | •    |      | •    |

| Input Voltage Range                                                                       | V <sub>DDQ</sub>       | 1.71 | 1.80 | 1.89 | V    |

| Output Voltage Setting                                                                    | V <sub>BG</sub>        | -    | 1.25 | -    | V    |

| Output Voltage Accuracy                                                                   | -                      | -2.0 | -    | 2.0  | %    |

| Under-voltage Detection Threshold (With respect to the output voltage)                    | V <sub>BGUV</sub>      | -    | -12  | -    | %    |

| Under-voltage Detection Threshold Hysteresis                                              | V <sub>BGUVH</sub>     | -    | 1.0  | -    | %    |

| Continuous Output Load Current                                                            |                        |      |      |      |      |

| Active Mode                                                                               | I <sub>BG</sub>        | -    | -    | 2.0  | mA   |

| Low Power Mode                                                                            | -                      | -    | -    | 40   | μA   |

| Current Limit                                                                             | I <sub>LIMBG</sub>     | -    | 94   | -    | mA   |

| Transient Load Change                                                                     | ∆l <sub>BG</sub>       | -    | -    | 1.0  | mA   |

| Power Supply Rejection Ratio (PSRR) (20 to 100 kHz, $I_{BG}$ = 1.5 mA, $V_{DDQ}$ = 1.8 V) | PSRR <sub>BG</sub>     | 50   | 60   | -    | dB   |

| Effective Quiescent Current Consumption                                                   | I <sub>QBG</sub>       |      |      |      | μA   |

| Active Mode                                                                               |                        | -    | -    | 18   |      |

| Low Power Mode                                                                            |                        | -    | -    | 10   |      |

## **Table 3. Static Electrical Characteristics**

$T_A$  = -40 °C to 85 °C,  $V_{PWR}$  = 3.0 to 4.4 V, typical external component values, and full load current range, unless otherwise noted. Typical values are characterized at  $V_{PWR}$  = 3.6 V and 25 °C.

| Characteristic                                                                                | Symbol                | Min   | Тур  | Max   | Unit |

|-----------------------------------------------------------------------------------------------|-----------------------|-------|------|-------|------|

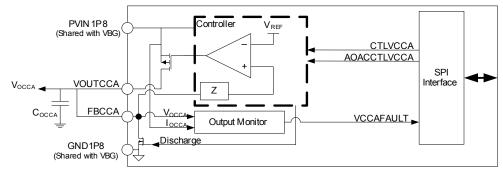

| /CCA ELECTRICAL CHARACTERISTICS                                                               |                       |       |      |       |      |

| Input Voltage Range                                                                           | V <sub>DDQ</sub>      | 1.71  | 1.80 | 1.89  | V    |

| Output Voltage Setting                                                                        | V <sub>CCA</sub>      | -     | 1.5  | -     | V    |

| Output Voltage Accuracy                                                                       | -                     | -2.0  | -    | 2.0   | %    |

| Under Voltage Detection Threshold (With respect to the output voltage)                        | V <sub>CCAUV</sub>    | -     | -12  | -     | %    |

| Under Voltage Detection Threshold Hysteresis                                                  | V <sub>CCAUVH</sub>   | -     | 1.0  | -     | %    |

| Continuous Output Load Current                                                                | I <sub>CCA</sub>      |       |      |       |      |

| Active Mode                                                                                   |                       | -     | -    | 150   | mA   |

| Low Power Mode                                                                                |                       | -     | -    | 3.0   | mA   |

| Current Limit                                                                                 | ILIMCCA               | -     | 225  | -     | mA   |

| Transient Load Change                                                                         | $\Delta I_{CCA}$      | -     | -    | 50    | mA   |

| Power Supply Rejection Ratio (PSRR) (20 to 100 kHz, $I_{CCA}$ = 112.5 mA, $V_{DDQ}$ = 1.8 V)  | PSRR <sub>CCA</sub>   | 50    | 60   | -     | dB   |

| Effective Quiescent Current Consumption                                                       | I <sub>QCCA</sub>     |       |      |       | μA   |

| Active Mode                                                                                   |                       | -     | -    | 18    |      |

| Low Power Mode                                                                                |                       | -     | -    | 10    |      |

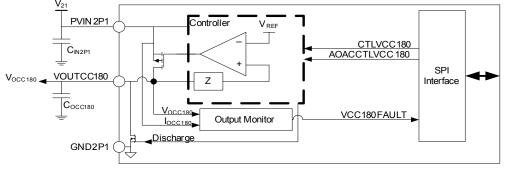

| CC180 ELECTRICAL CHARACTERISTICS                                                              |                       |       |      |       |      |

| Input Voltage Range                                                                           | V <sub>21</sub>       | 1.995 | 2.1  | 2.205 | V    |

| Output Voltage Setting                                                                        | V <sub>CC180</sub>    | -     | 1.8  | -     | V    |

| Output Voltage Accuracy                                                                       | -                     | -5.0  | -    | 5.0   | %    |

| Under-voltage Detection Threshold (With respect to the output voltage)                        | V <sub>CC180UV</sub>  | -     | -12  | -     | %    |

| Under-voltage Detection Threshold Hysteresis                                                  | V <sub>CC180UVH</sub> | -     | 1.0  | -     | %    |

| Continuous Output Load Current                                                                | I <sub>CC180</sub>    |       |      |       |      |

| Active Mode                                                                                   |                       | -     | -    | 390   | mA   |

| Low Power Mode                                                                                |                       | -     | -    | 7.8   | mA   |

| Current Limit                                                                                 | I <sub>LIMCC180</sub> | -     | 585  | -     | mA   |

| Transient Load Change                                                                         | $\Delta I_{CC180}$    | -     | -    | 350   | mA   |

| Power Supply Rejection Ratio (PSRR) (20 to 100 kHz, $I_{CC180}$ = 292.5 mA, $V_{21}$ = 2.1 V) | PSRR <sub>CC180</sub> | 50    | 60   | -     | dB   |

| Effective Quiescent Current Consumption                                                       | I <sub>QCC180</sub>   |       |      |       | μA   |

| Active Mode                                                                                   |                       | -     | -    | 18    |      |

| Low Power Mode                                                                                |                       | -     | -    | 10    |      |

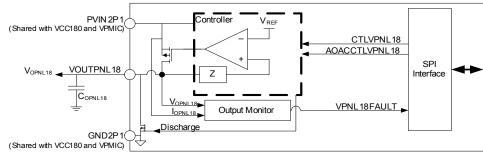

| /PNL18 ELECTRICAL CHARACTERISTICS SPECIFICATION                                               |                       |       |      |       |      |

| Input Voltage Range                                                                           | V <sub>21</sub>       | 1.995 | 2.1  | 2.205 | V    |

| Output Voltage Setting                                                                        | V <sub>PNL18</sub>    | -     | 1.8  | -     | V    |

| Output Voltage Accuracy                                                                       | -                     | -5.0  | -    | 5.0   | %    |

-

-

%

%

-12

1.0

-

-

V<sub>PNL18UV</sub>

V<sub>PNL18UVH</sub>

Under-voltage Detection Threshold (With respect to the output voltage)

Under-voltage Detection Threshold Hysteresis

## Table 3. Static Electrical Characteristics

$T_A$  = -40 °C to 85 °C,  $V_{PWR}$  = 3.0 to 4.4 V, typical external component values, and full load current range, unless otherwise noted. Typical values are characterized at  $V_{PWR}$  = 3.6 V and 25 °C.

| Characteristic                                                                                                                      | Symbol                   | Min   | Тур | Max   | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------|-----|-------|------|

| Continuous Output Load Current                                                                                                      |                          |       |     |       | mA   |

| Active Mode                                                                                                                         | I <sub>PNL18</sub>       | -     | -   | 210   |      |

| Low Power Mode                                                                                                                      |                          | -     | -   | 4.2   |      |

| Current Limit                                                                                                                       | I <sub>LIMPNL18</sub>    | -     | 315 | -     | mA   |

| Transient Load Change                                                                                                               | $\Delta I_{PNL18}$       | -     | -   | 100   | mA   |

| Power Supply Rejection Ratio (PSRR) (20 to 100 kHz, $\rm I_{PNL18}$ = 157.5 mA, $\rm V_{21}$ = 2.1 V)                               | PSRR <sub>PNL18</sub>    | 50    | 60  | -     | dB   |

| Effective Quiescent Current Consumption                                                                                             | I <sub>QPNL18</sub>      |       |     |       | μA   |

| Active Mode                                                                                                                         |                          | -     | -   | 18    |      |

| Low Power Mode                                                                                                                      |                          | -     | -   | 10    |      |

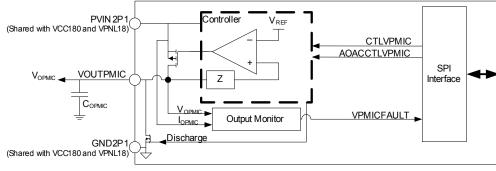

| /PMIC ELECTRICAL CHARACTERISTICS                                                                                                    |                          |       |     |       |      |

| Input Voltage Range                                                                                                                 | V <sub>21</sub>          | 1.995 | 2.1 | 2.205 | V    |

| Output Voltage Setting                                                                                                              | V <sub>PMIC</sub>        | -     | 1.8 | -     | V    |

| Output Voltage Accuracy                                                                                                             | -                        | -5.0  | -   | 5.0   | %    |

| Under-voltage Detection Threshold                                                                                                   | V <sub>PMICUV</sub>      | -     | -12 | -     | %    |

| (With respect to the output voltage)                                                                                                |                          |       |     |       |      |

| Under Voltage Detection Threshold Hysteresis                                                                                        | V <sub>PMICUVH</sub>     | -     | 1.0 | -     | %    |

| Continuous Output Load Current                                                                                                      | I <sub>PMIC</sub>        |       |     |       | mA   |

| Active Mode                                                                                                                         | 1 Milo                   | -     | -   | 100   |      |

| Low Power Mode                                                                                                                      |                          | -     | -   | 2.0   |      |

| Current Limit                                                                                                                       | ILIMPMIC                 | -     | 150 | -     | mA   |

| Transient Load Change                                                                                                               | Δl <sub>PMIC</sub>       | -     | -   | 20    | mA   |

| Power Supply Rejection Ratio (PSRR) (20 to 100 kHz, $I_{PMIC}$ = 75 mA, $V_{21}$ = 2.1 V)                                           | PSRR <sub>PMIC</sub>     | 50    | 60  | -     | dB   |

| Effective Quiescent Current Consumption                                                                                             |                          |       |     |       | μA   |

| Active Mode                                                                                                                         | I <sub>QPMIC</sub>       | -     | -   | 18    |      |

| Low Power Mode                                                                                                                      |                          | -     | -   | 10    |      |

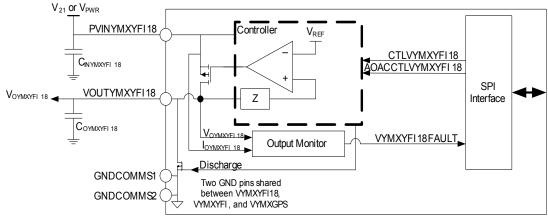

| /YMXYFI18 ELECTRICAL CHARACTERISTICS                                                                                                |                          |       |     |       |      |

| Input Voltage Range                                                                                                                 |                          |       |     |       | V    |

| Supplied by V <sub>21</sub> DC/DC                                                                                                   | V <sub>21</sub>          | 1.995 | 2.1 | 2.205 |      |

| Supplied by V <sub>PWR</sub>                                                                                                        | V <sub>PWR</sub>         | 3.0   | 3.6 | 4.4   |      |

| Output Voltage Setting                                                                                                              | V <sub>YMXYFI18</sub>    | -     | 1.8 | -     | V    |

| Output Voltage Accuracy                                                                                                             | -                        | -5.0  | -   | 5.0   | %    |

| Under-voltage Detection Threshold (With respect to the output voltage)                                                              | V <sub>YMXYFI18UV</sub>  | -     | -12 | -     | %    |

| Under-voltage Detection Threshold Hysteresis                                                                                        | V <sub>YMXYFI18UVH</sub> | -     | 1.0 | -     | %    |

| Continuous Output Load Current                                                                                                      | I <sub>YMXYFI18</sub>    |       |     |       | mA   |

| Active Mode                                                                                                                         | THE COLOR                | -     | -   | 200   |      |

| Low Power Mode                                                                                                                      |                          | -     | -   | 4.0   |      |

| Current Limit                                                                                                                       | I <sub>LIMYMXYFI18</sub> | -     | 300 | -     | mA   |

| Transient Load Change                                                                                                               | ΔI <sub>YMXYFI18</sub>   | -     | -   | 100   | mA   |

| Power Supply Rejection Ratio (PSRR) (20 to 100 kHz, $I_{YMXYF118}$ = 150 mA), (V <sub>21</sub> = 2.1 V or V <sub>PWR</sub> = 3.6 V) | PSRR <sub>YMXYFI18</sub> | 40    | -   | -     | dB   |

900841

## **Table 3. Static Electrical Characteristics**

| Characteristic                                                                                                                                     | Symbol                     | Min   | Тур | Max   | Unit              |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------|-----|-------|-------------------|

| Output Noise (10 Hz to 100 kHz, $I_{YMXYFI18}$ = 200 mA), (V <sub>21</sub> = 2.1 V or V <sub>PWR</sub> = 3.6 V)                                    | V <sub>NOISEYMXYFI18</sub> | -     | -   | 40    | μV <sub>RMS</sub> |

| Effective Quiescent Current Consumption                                                                                                            | I <sub>QYMXYFI18</sub>     |       |     |       | μA                |

| Active Mode                                                                                                                                        |                            | -     | -   | 18    |                   |

| Low Power Mode                                                                                                                                     |                            | -     | -   | 10    |                   |

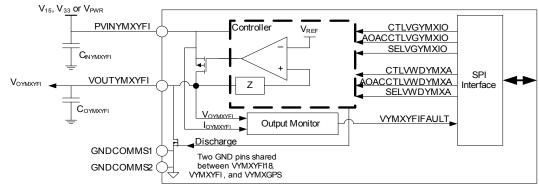

| VYMXYFI ELECTRICAL CHARACTERISTICS                                                                                                                 |                            |       |     |       |                   |

| Input Voltage Range                                                                                                                                |                            |       |     |       | V                 |

| Supplied by V <sub>15</sub> DC/DC (WiFiBT Applications)                                                                                            | V <sub>15</sub>            | 1.425 | 1.5 | 1.575 |                   |

| Supplied by V <sub>33</sub> DC/DC (WiMAX Applications)                                                                                             | V <sub>33</sub>            | 3.168 | 3.3 | 3.432 |                   |

| Supplied by V <sub>PWR</sub> (WiMAX Applications)                                                                                                  | V <sub>PWR</sub>           | 3.0   | 3.6 | 4.4   |                   |

| Output Voltage Setting                                                                                                                             | V <sub>YMXYFI</sub>        |       |     |       | V                 |

| WiFiBT Applications                                                                                                                                |                            | -     | 1.2 | -     |                   |

| WiMAX Applications                                                                                                                                 |                            | -     | 2.5 | -     |                   |

| Output Voltage Accuracy                                                                                                                            | -                          | -5.0  | -   | 5.0   | %                 |

| Under-voltage Detection Threshold (With respect to the output voltage)                                                                             | V <sub>YMXYFIUV</sub>      | -     | -12 | -     | %                 |

| Under Voltage Detection Threshold Hysteresis                                                                                                       | V <sub>YMXYFIUVH</sub>     | -     | 1.0 | -     | %                 |

| Continuous Output Load Current                                                                                                                     | I <sub>YMXYFI</sub>        |       |     |       | mA                |

| Active Mode (WiFiBT Applications)                                                                                                                  |                            | -     | -   | 60    |                   |

| Active Mode (WiMAX Applications)                                                                                                                   |                            | -     | -   | 150   |                   |

| Low Power Mode                                                                                                                                     |                            | -     | -   | 1.2   |                   |

| Current Limit                                                                                                                                      | I <sub>LIMYMXYFI</sub>     | -     | 225 | -     | mA                |

| Transient Load Change                                                                                                                              | $\Delta I_{YMXYFI}$        |       |     |       | mA                |

| WiFiBT Applications                                                                                                                                |                            | -     | -   | 32    |                   |

| WiMAX Applications                                                                                                                                 |                            | -     | -   | 130   |                   |

| Power Supply Rejection Ratio (PSRR) (20 kHz, $I_{YMXYFI}$ = 45 mA), (V <sub>15</sub> = 1.5) (WiFiBT Applications)                                  | PSRR <sub>YMXYFI</sub>     | 50    | 60  | -     | dB                |

| Power Supply Rejection Ratio (PSRR) (100 kHz, $I_{YMXYFI}$ = 112.5 mA), (V <sub>33</sub> = 3.3 V or V <sub>PWR</sub> = 3.6 V) (WiMAX Applications) | PSRR <sub>YMXYFI</sub>     | 40    | -   | -     | dB                |

| Output Noise (10 Hz to 100 kHz, $I_{YMXYFI}$ = 60 mA), (V <sub>15</sub> = 1.5 V) (WiFiBT Applications)                                             | V <sub>NOISEYMXYFI</sub>   | -     | -   | 40    | μV <sub>RMS</sub> |

| Output Noise (10 Hz to 100 kHz, $I_{YMXYFI}$ = 150 mA), (V <sub>33</sub> = 3.3 V or V <sub>PWR</sub> = 3.6 V) (WiMAX Applications)                 | V <sub>NOISEYMXYFI</sub>   | -     | -   | 40    | μV <sub>RMS</sub> |

| Effective Quiescent Current Consumption                                                                                                            | I <sub>QYMXYFI</sub>       |       |     |       | μA                |

| Active Mode                                                                                                                                        |                            | -     | -   | 18    |                   |

| Low Power Mode                                                                                                                                     |                            | -     | -   | 10    |                   |

## Table 3. Static Electrical Characteristics

| Characteristic                                                                                                                                          | Symbol                   | Min   | Тур  | Max   | Unit             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------|------|-------|------------------|

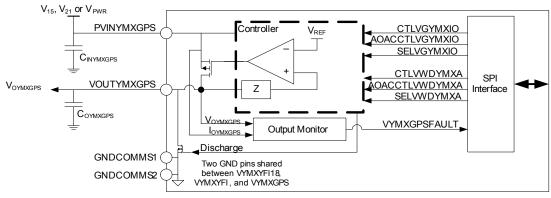

| /YMXGPS ELECTRICAL CHARACTERISTICS                                                                                                                      | -                        |       |      |       |                  |

| Input Voltage Range                                                                                                                                     |                          |       |      |       | V                |

| Supplied by V <sub>15</sub> DC/DC (WiMAX Applications)                                                                                                  | V <sub>15</sub>          | 1.52  | 1.6  | 1.68  |                  |

| Supplied by V <sub>21</sub> DC/DC (GPS Applications)                                                                                                    | V <sub>21</sub>          | 1.995 | 2.1  | 2.205 |                  |

| Supplied by V <sub>PWR</sub> (GPS Applications)                                                                                                         | V <sub>PWR</sub>         | 3.0   | 3.6  | 4.4   |                  |

| Output Voltage Setting                                                                                                                                  | V <sub>YMXGPS</sub>      |       |      |       | V                |

| WiMAX Applications                                                                                                                                      |                          | -     | 1.3  | -     |                  |

| GPS Applications                                                                                                                                        |                          | -     | 1.8  | -     |                  |

| Output Voltage Accuracy                                                                                                                                 | -                        | -5.0  | -    | 5.0   | %                |

| Under-voltage Detection Threshold (With respect to the output voltage)                                                                                  | V <sub>YMXGPSUV</sub>    | -     | -12  | -     | %                |

| Under-voltage Detection Threshold Hysteresis                                                                                                            | V <sub>YMXGPSUVH</sub>   | -     | 1.0  | -     | %                |

| Continuous Output Load Current                                                                                                                          | I <sub>YMXGPS</sub>      |       |      |       | mA               |

| Active Mode (WIMAX Applications)                                                                                                                        |                          | -     | -    | 350   |                  |

| Active Mode (GPS Applications)                                                                                                                          |                          | -     | -    | 170   |                  |

| Low Power Mode                                                                                                                                          |                          | -     | -    | 3.4   |                  |

| Current Limit                                                                                                                                           | I <sub>LIMYMXGPS</sub>   | -     | 525  | -     | mA               |

| Transient Load Change                                                                                                                                   | ΔI <sub>YMXGPS</sub>     |       |      |       | mA               |

| WiMAX Applications                                                                                                                                      |                          | -     | -    | 200   |                  |

| GPS Applications                                                                                                                                        |                          | -     | -    | 130   |                  |

| Power Supply Rejection Ratio (PSRR) (20 kHz, $I_{YMXGPS}$ = 262.5 mA), (V <sub>15</sub> = 1.6 V) (WiMAX Applications)                                   | PSRR <sub>YMXGPS</sub>   | 50    | 60   | -     | dB               |

| Power Supply Rejection Ratio (PSRR), (20 to 100 kHz, $I_{YMXGPS}$ = 127.5 mA), (V <sub>21</sub> = 2.1 V or V <sub>PWR</sub> = 3.6 V) (GPS Applications) | PSRR <sub>YMXGPS</sub>   | 40    | -    | -     | dB               |

| Output Noise (10 Hz to 100 kHz, $I_{YMXGPS}$ = 350 mA), (V <sub>15</sub> = 1.6 V) (WiMAX Applications)                                                  | V <sub>NOISEYMXGPS</sub> | -     | -    | 40    | μV <sub>RM</sub> |

| Output Noise (10 Hz to 100 kHz, $I_{YMXGPS}$ = 170 mA), (V <sub>21</sub> = 2.1 V or V <sub>PWR</sub> = 3.6 V) (GPS Applications)                        | V <sub>NOISEYMXGPS</sub> | -     | -    | 40    | μV <sub>RM</sub> |

| Effective Quiescent Current Consumption                                                                                                                 | I <sub>QYMXGPS</sub>     |       |      |       | μA               |

| Active Mode                                                                                                                                             |                          | -     | -    | 18    |                  |

| Low Power Mode                                                                                                                                          |                          | -     | -    | 10    |                  |

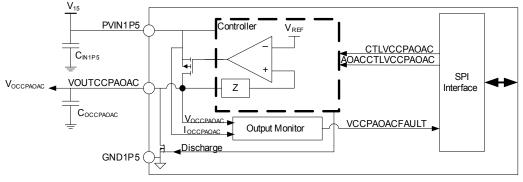

| CCPAOAC ELECTRICAL CHARACTERISTICS                                                                                                                      |                          |       |      |       |                  |

| Input Voltage Range                                                                                                                                     | V <sub>15</sub>          | 1.425 | 1.5  | 1.680 | V                |

| Output Voltage Setting                                                                                                                                  |                          | -     | 1.05 | -     | V                |

| input voltage italige                                                  | V <sub>15</sub>         | 1.425 | 1.5   | 1.000 | v  |

|------------------------------------------------------------------------|-------------------------|-------|-------|-------|----|

| Output Voltage Setting                                                 | V <sub>CCPAOAC</sub>    | -     | 1.05  | -     | V  |

| Output Voltage Accuracy                                                | -                       | -5.0  | -     | 5.0   | %  |

| Under-voltage Detection Threshold (With respect to the output voltage) | V <sub>CCPAOACUV</sub>  | -     | -12   | -     | %  |

| Under-voltage Detection Threshold Hysteresis                           | V <sub>CCPAOACUVH</sub> | -     | 1.0   | -     | %  |

| Continuous Output Load Current                                         | I <sub>CCPAOAC</sub>    |       |       |       | mA |

| Active Mode                                                            |                         | -     | -     | 155   |    |

| Low Power Mode                                                         |                         | -     | -     | 3.1   |    |

| Current Limit                                                          | ILIMCCPAOAC             | -     | 232.5 | -     | mA |

## **Table 3. Static Electrical Characteristics**

| Characteristic                                                                                      | Symbol                  | Min   | Тур  | Max   | Unit |

|-----------------------------------------------------------------------------------------------------|-------------------------|-------|------|-------|------|

| Transient Load Change                                                                               |                         | -     | -    | 50    | mA   |

| Power Supply Rejection Ratio (PSRR) (20 to 100 kHz, $I_{CCPAOAC}$ = 116 mA, $V_{15}$ = 1.5 V)       | PSRR <sub>CCPAOAC</sub> | 50    | 60   | -     | dB   |

| Effective Quiescent Current Consumption                                                             | I <sub>QCCPAOAC</sub>   |       |      |       | μA   |

| Active Mode                                                                                         |                         | -     | -    | 18    |      |

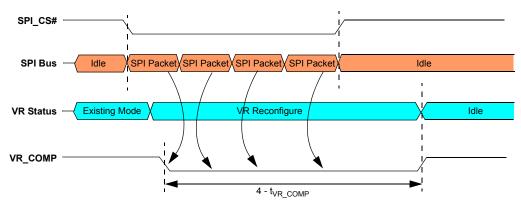

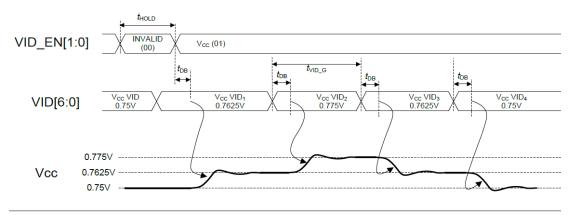

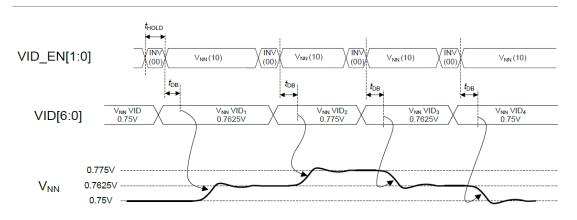

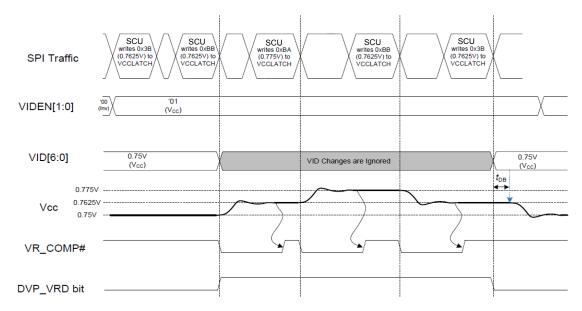

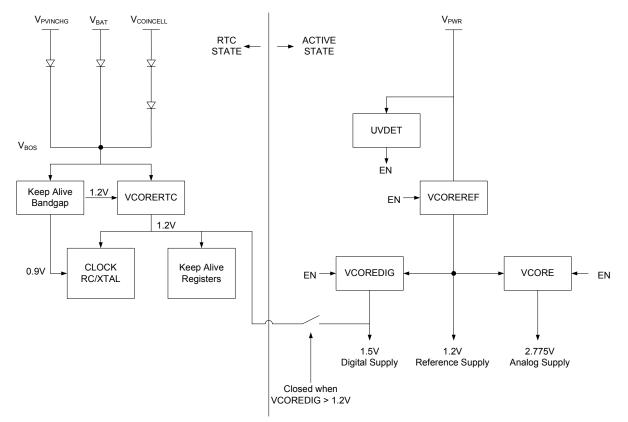

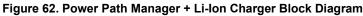

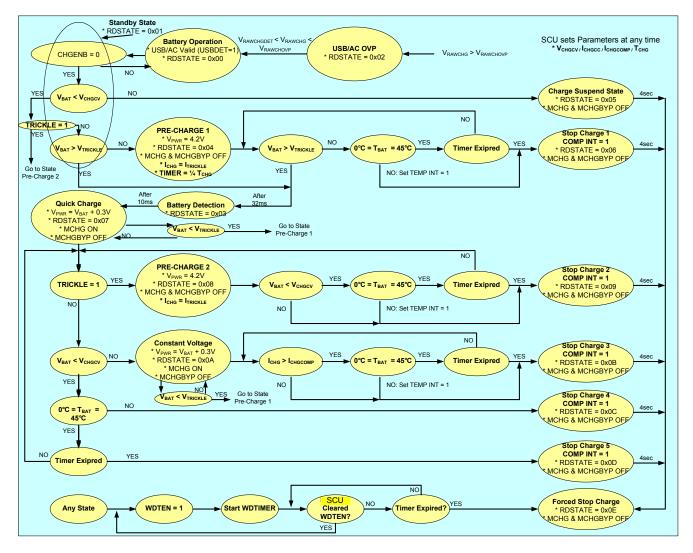

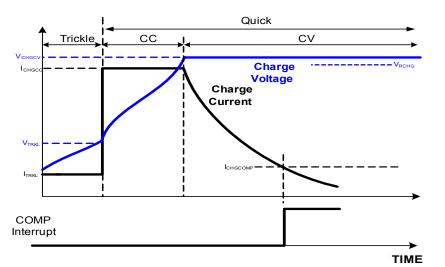

| Low Power Mode                                                                                      |                         | -     | -    | 10    |      |